This page gives an overview of Soft IP's DMA(AXI DMA/CDMA/VDMA) driver, which is available as part of the

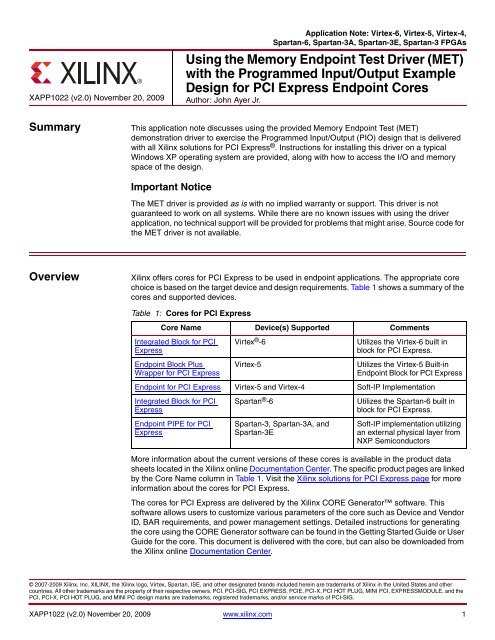

This page is intended to give more details on the Xilinx drivers for Linux, such as testing, how to use the drivers, known issues, etc. The drivers included in the kernel tree are intended to run on ARM (Zynq, Zynq Ultrascale+ MPSoC) and MicroBlaze Linux. Commits: d4df1d5 dma: xilinxdma: check for channel idle state before submitting the dma descriptor. 05ce73d dma: xilinxdma: Fix bug in multiple frame stores scenario in vdma 3794829 dma: xilinxdma: Fix race condition in the driver for multiple descriptor scenario for axidma. PCI Driver for Xilinx All Programmable FPGA Jungo Connectivity Ltd. Is a Xilinx Alliance Program Member tier company. The WinDriver™ product line has enhanced supports for Xilinx devices, and enables you to focus on your driver’s added-value functionality, instead of. Xilinx GitHub link to Linux drivers and software; Windows binary driver files and the associated document. The provided pdf document is for an older version of the driver files. However, the application section still applies to the latest driver files attached with this answer record. The document will be updated in a future release. Xilinx Answer 65444 – Xilinx PCI Express DMA Drivers and Software Guide 4 Here is an example of how to read 4 bytes from AXI-Lite interface from offset (0x0000). Xdmarw.exe user read 0 –l 4.

Xilinx Linux distribution and in open source linux as drivers/dma/xilinx_dma.cAXI DMA

The AXI Direct Memory Access (AXI DMA) IP provides high-bandwidth direct memory access between memory and AXI4-Stream-type target peripherals. Its optional scatter gather capabilities also offload data movement tasks from the Central Processing Unit (CPU) in processor-based systems. Initialization, status, and management registers are accessed through an AXI4-Lite slave interface.- AXI4 and AXI4-Stream compliant

- Optional Scatter/Gather (SG) DMA support. When Scatter/gather mode is not selected the IP operates in Simple DMA mode.

- Primary AXI4 Memory Map and AXI4-Stream data width support of 32, 64, 128, 256, 512, and 1024 bits

- Optional Data Re-Alignment Engine

- Optional AXI Control and Status Streams

- Multi-channel mode

- Optional Keyhole support

- Optional Micro DMA mode support

- Support for upto 64-bit Addressing

Features supported in driver

- Optional Scatter/Gather (SG) DMA support. When Scatter/gather mode is not selected the IP operates in Simple DMA mode.

- Primary AXI4 Memory Map and AXI4-Stream data width support of 32, 64, 128, 256, 512, and 1024 bits

- Optional Data Re-Alignment Engine

- Optional AXI Control and Status Streams

- Multi-channel mode

- 64-bit Addressing support

AXI CDMA

The AXI CDMA provides high-bandwidth direct memory access (DMA) between a memory mapped source address and a memory mapped destination address using the AXI4 protocol. An optional Scatter Gather (SG) feature can be used to offload control and sequencing tasks from the System CPU. Initialization, status, and control registers are accessed through an AXI4-Lite slave interface.- AXI4 Compliant

- Primary AXI Memory Map data width support of 32, 64, 128, and 256 bits

- Primary AXI Stream data width support of 8, 16, 32, 64, 128, and 256 bits

- Optional Data Re-Alignment Engine

- Optional Gen-Lock Synchronization

- Independent, asynchronous channel operation

- Provides Simple DMA only mode and an optional hybrid mode supporting both Simple DMA and Scatter-Gather automation

- Optional Store and Forward operation mode with internal Data FIFO (First In First Out)

Features supported in driver

- Optional Scatter/Gather (SG) DMA support. When Scatter/gather mode is not selected the IP operates in Simple DMA mode.

- Primary AXI4 Memory Map and AXI4-Stream data width support of 32, 64, 128, 256, 512, and 1024 bits

- Optional Data Re-Alignment Engine

- 64-bit Addressing Support

- Simple DMA mode

- Scatter-Gather DMA mode

AXI VDMA

The AXI Video Direct Memory Access (AXI VDMA) core is a soft Xilinx IP core that provides high-bandwidth direct memory access between memory and AXI4-Stream type video target peripherals. The core provides efficient two dimensional DMA operations with independent asynchronous read and write channel operation. Initialization, status, interrupt and management registers are accessed through an AXI4-Lite slave interface.- High-bandwidth direct memory access for video streams

- Efficient two-dimensional DMA operations

- Independent, asynchronous read and write channel operation

- Gen-Lock frame buffer synchronization

- Supports maximum of 32 frame buffers

- Supports dynamic video format changes

- Configurable Burst Size and Line Buffer depth for efficient video streaming

- Processor accessible initialization, status, interrupt and management registers

- Primary AXI Stream data width support for multiples of 8-bits: 8, 16, 24, 32, etc. up to 1024 bits

- 64-bit Addressing

Features supported in driver

- 2-D Operations

- Support for maximum 32 frame buffers

- 64-bit Addressing

- Gen-lock frame buffer synchronization

AXI DMA

- No support for Keyhole feature

AXI CDMA

- None

AXI VDMA

- Configurable Burst Size and Line Buffer depth for efficient video streaming

CONFIG_DMADEVICES

CONFIG_XILINX_DMA

CONFIG_XILINX_DMAThe driver is available at,

https://github.com/Xilinx/linux-xlnx/blob/master/drivers/dma/xilinx/xilinx_dma.c

The device tree node for AXI DMA/CDMA/VDMA will be automatically generated, if the core is configured in the HW design, using the Device Tree BSP.

Steps to generate device-tree is documented here,

http://www.wiki.xilinx.com/Build+Device+Tree+Blob

And a sample binding is shown below and the description of DT property is documented here

AXI DMA

AXI CDMA

AXI VDMA

AXI DMA

A separate test case is provided to test the functionality of IP which assumes the IP streaming interfaces are connected back-to-back in the HW design. The test client is designed to transfer the data on the streaming interface (MM2S) and compares the data received on another interface (S2MM) which is loopback'ed. This test client is available in the Linux source at,https://github.com/Xilinx/linux-xlnx/blob/master/drivers/dma/xilinx/axidmatest.c

NOTE: In ZynqMP vivado design it is mandatory to enable high address=1 (Zynq Ultrsacale+ MPSoC customization-> PS-PL configuration-> Address Fragementation-> High Address) and set AXI DMA adress width=40 bits.

For detail please refer: http://www.wiki.xilinx.com/PL+Masters

The test client can be configured in the ZynqMPSOC/Zynq/Microblaze kernel as either module or in-built,

Device-tree Node for test client

Running the test client will display the message when test is successful,

AXI CDMA

A separate test case is provided to test the functionality of IP which is designed to read the data from one location of memory and compare the data after copying data to other location of memory. This test client is available in the Linux source at,https://github.com/Xilinx/linux-xlnx/blob/master/drivers/dma/xilinx/cdmatest.c

The test client can be configured in the Zynq/Microblaze kernel as either module or in-built,

Device-tree Node for test client

Running the test client will display the message when test is successful,

AXI VDMA

A separate test case is provided to test the functionality of IP which assumes the IP streaming interfaces are connected back-to-back in the HW design. The test client is designed to transfer the data on the streaming interface (MM2S) and compares the data received on another interface (S2MM) which is loopback'ed. This test client is available in the Linux source at,https://github.com/Xilinx/linux-xlnx/blob/master/drivers/dma/xilinx/vdmatest.c

The test client can be configured in the Zynq/Microblaze kernel as either module or in-built,

Device-tree Node for test client

Running the test client will display the message when test is successful,

The current driver available in the xilinx linux git is in sync with the open source 4.9 kernel driver except for the following

- Add idle checks across the driver for all the DMA's (AXI DMA/CDMA/VDMA) before submitting the descriptor.

- Fix bug in multiple frame stores scenario in vdma

- Fix race condition in the driver for multiple descriptor scenarios for axidma.

Summary:

- Mainlined the driver

- Fixed the issues as per the commit ID

- Deleted the AXI DMA/CDMA driver and Merged the AXI DMA/CDMA code with the VDMA driver

- Merged all the 3 DMA's drivers into a single driver

Commits:

commit dma: xilinx: axidma: Fix race condition in the cyclic dma mode

dma: xilinx: axidma: Fix race condition in the cyclic dma mode

commit: vdma: sync driver with mainline

commit: vdma: sync driver with mainline

commit: dma: xilinx: Delete AXI DMA driver

dma: xilinx: Delete AXI DMA driver

commit: dma: xilinx: Delete AXI CDMA driver

dma: xilinx: Delete AXI CDMA driver

commit: dma: xilinx: Use dma_poll_zalloc

dmaengine: vdma: Use dma_pool_zalloc

commit: dmaengine: vdma: Rename xilinx_vdma_prefix to xilinx_dma

dmaengine: vdma: Rename xilinx_vdma_ prefix to xilinx_dma

commit: dmaengine: vdma: Add support for AXI DMA driver

dmaengine: vdma: Add Support for Xilinx AXI Direct Memory Access Engine

commit: dmaengine: vdma: Add support for AXI CDMA driver

dmaengine: vdma: Add Support for Xilinx AXI Central Direct Memory Acc… …ess Engine

commit: dmaengine: vdma: Add config sructure to differentiate dmas

dmaengine: vdma: Add config structure to differentiate dmas

commit: dmaengine: vdma: Add clock support

dmaengine: vdma: Add clock support

commit: dmaengine: don't crash when bad DMA channel is requested.

dmaengine: vdma: don't crash when bad channel is requested

commit: dmaengine: Add support for cyclic dma mode

dmaengine: vdma: Add support for cyclic dma mode

commit: dmaengine: use dma_pool_zalloc

dmaengine: vdma: Use dma_pool_zalloc

commit: dmaengine: Fix compilation warning in cyclic DMA mode

dmaengine: vdma: Fix compilation warning in cyclic dma mode

commit: dmaengine: Add 64-bit Addressing support for AXI DMA

dmaengine: vdma: Add 64 bit addressing support for the axi dma

commit: dmaengine: Add 64-bit Addressing support for AXI CDMA

dmaengine: vdma: Add 64 bit addressing support for the axi cdma

commit: dmaengine: Add support for multi channel mode for AXI DMA

dmaengine: vdma: Add support for mulit-channel dma mode

commit: dmaengine: Rename driver and config

dmaengine: xilinx: Rename driver and config

commit: dmaengine: use different channel names for each DMA

dmaengine: xilinx: Use different channel names for each dma

commit: dmaengine: Fix race condition in AXI DMA cyclic Mode

Xilinx Driver Win 10

dmaengine: xilinx: Fix race condition in axi dma cyclic dma modecommit: dma: update test client depends configs

dma: xilinx: Update test clients depends config option

commit: Check for channel Idle state before submitting descriptors

dma: xilinx: Check for channel idle state before submitting dma descr…

2016.4

- None

2017.1

Summary:

- Add idle checks across the driver for all the DMA's (AXI DMA/CDMA/VDMA) before submitting the descriptor.

- Fix bug in multiple frame stores scenario in vdma

- Fix race condition in the driver for multiple descriptor scenario for axidma.

Commits:

d4df1d5 dma: xilinx_dma: check for channel idle state before submitting the dma descriptor.

05ce73d dma: xilinx_dma: Fix bug in multiple frame stores scenario in vdma

3794829 dma: xilinx_dma: Fix race condition in the driver for multiple descriptor scenario for axidma.

2017.2

- None

2017.3

Summary:

- Fix issues with dma_get_slave_caps API for AXI DMA configuration.

- Fix issues with vdma mulit fstore configuration.

ed2ee32 dma: xilinx: Fix issues with vdma mulit fstore configuration

54c8b75dma: xilinx: Fix dma_get_slave_caps gaps

2017.4

Summary:

- Added support for memory sg transactions for cdma

- Fixed race conditions in the driver for cdma

- Differentiate probe based on IP type.

- Fix compiler warning.

9e8f5fc dma: xilinx: Add support for memory sg transactions for cdma

b3fe111 dma: xilinx: Fix race conditions in the driver for cdma.

Xilinx Drivers Linux

61a18fd dma: xilinx: Differentiate probe based on the IP type.Xilinx Xdma Driver

322bd63dma: xilinx: xilinx_dma: Fix compilation warning.

Xilinx Platform Cable Usb Driver